Სარჩევი:

- ავტორი John Day day@howwhatproduce.com.

- Public 2024-01-30 10:18.

- ბოლოს შეცვლილი 2025-06-01 06:09.

ამ ინსტრუქციურად, ჩვენ ვაპირებთ VHDL- ში ნულიდან შევქმნათ SPI Bus Master.

ნაბიჯი 1: SPI- ის მიმოხილვა

- SPI არის სინქრონული სერიული ავტობუსი

- მისმა პოპულარობამ და სიმარტივემ ის დე ფაქტო სტანდარტად აქცია სერიულ კომუნიკაციაში

- სრული დუპლექსის ავტობუსი

- მარტივი პროტოკოლი და უსწრაფესი სერიული ავტობუსი

ნაბიჯი 2: დიზაინის სპეციფიკაციები

ეს არის SPI Master- ის სპეციფიკაციები, რომელსაც ჩვენ ვგეგმავთ:

- მხარს უჭერს ოპერაციის ოთხივე რეჟიმს; დინამიურად კონფიგურირებადი

- საათი ჩართავს ენერგიის დაზოგვის კონტროლს

- სტატისტიკურად კონფიგურირებადი სიტყვის სიგრძე და სიჩქარე

- ერთჯერადი შეწყვეტა როგორც გადაცემის, ასევე მიღებისთვის

ნაბიჯი 3: გაშვება

პირველ რიგში, ჩვენს IP- ს უნდა ჰქონდეს ორი ინტერფეისი. ერთი არის სერიული ინტერფეისი და მეორე არის პარალელური ინტერფეისი. სერიული ინტერფეისი შედგება SPI- ის დე ფაქტო სტანდარტული სიგნალებისგან: MOSI, MISO, SS, SCLK.

MOSI- ს ზოგჯერ SDO ეწოდება და MISO- ს ზოგჯერ SDI.

სერიული ინტერფეისი გამოიყენება გარე პერიფერიულ მოწყობილობებთან, ანუ SPI მონებისათვის.

პარალელური ინტერფეისი გამოიყენება ჩვენს მასპინძელთან, ანუ მიკროკონტროლერთან ან მიკროპროცესორთან კომუნიკაციისთვის, რომელიც რეალურად ეუბნება ოსტატს რა მონაცემები უნდა იყოს სერიულად გადაცემული და მიღებული სერიული ხაზების საშუალებით. ანუ, ყველა მონაცემთა ავტობუსი ეკუთვნის პარალელურ ინტერფეისს.

ჩვენ გვაქვს გლობალური საათი, რომელიც ამოძრავებს შიდა SPI ლოგიკას, ასევე SCLK, რომელსაც ჩვენ შინაგანად ვქმნით.

ჩვენ ასევე გვაქვს გარკვეული საკონტროლო სიგნალები, როგორიცაა ჩაწერის ჩართვა, საათის ჩართვა. შეწყვეტის და სტატუსის სხვა სიგნალები.

ვინაიდან ჩვენ უნდა გავუმკლავდეთ კონტროლის რთულ პირობებს, უფრო ადვილია ისეთი სერიული საკომუნიკაციო IP- ების შემუშავება, როგორიცაა FSM. ჩვენ ასევე შეიმუშავებს SPI სამაგისტრო როგორც FSM ასევე. FSM ამოძრავებს სხვა შიდა საათს, რომელიც ორჯერ არის SCLK. ეს შიდა საათი გენერირდება გლობალური საათის სინქრონული მრიცხველების გამოყენებით.

ყველა საკონტროლო სიგნალს, რომელიც გადაკვეთს საათის დომენებს, აქვს სინქრონიზატორი უფრო უსაფრთხო მხარეს.

ნაბიჯი 4: SPI Master Core და სიმულაციური ტალღების ფორმების RTL ხედი

ეს არის შიშველი RTL დიზაინი, რომელსაც არ აქვს გამოყენებული FPGA IP. აქედან გამომდინარე, ეს არის სრულად პორტატული კოდი ნებისმიერი FPGA- სთვის.

გირჩევთ:

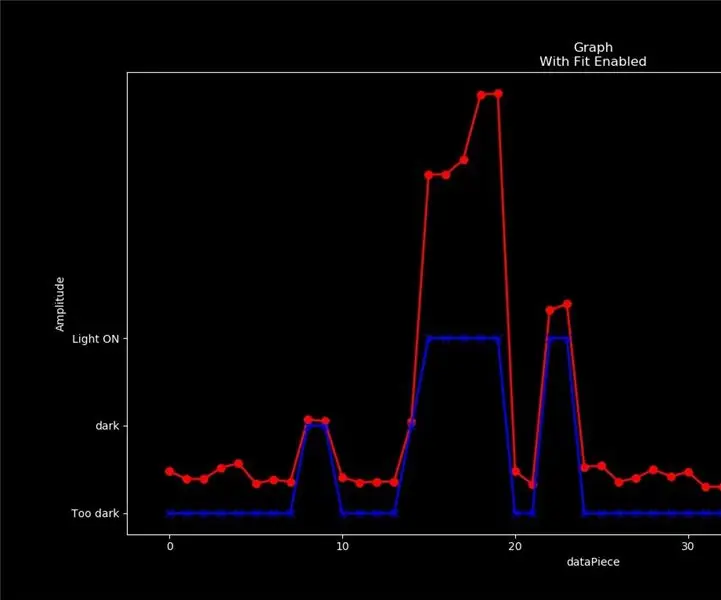

სინათლის ინტენსივობის შეთქმულება არდუინოს და პითონის არდუინოს სამაგისტრო ბიბლიოთეკის გამოყენებით: 5 ნაბიჯი

სინათლის ინტენსივობის შეთქმულება არდუინოს და პითონის არდუინოს სამაგისტრო ბიბლიოთეკის გამოყენებით: არდუინო არის ეკონომიური, მაგრამ მაღალეფექტური და ფუნქციონალური ინსტრუმენტი, ჩაშენებულ C- ში პროგრამირება ხდის პროექტების დამღლელ პროცესს! პითონის Arduino_Master მოდული ამარტივებს ამას და გვაძლევს საშუალებას გამოვთვალოთ, ამოიღოთ ნაგვის მნიშვნელობები

VHDL– ში მარტივი ოთხმხრივი კომპაქტური ქეში კონტროლერის დიზაინი: 4 ნაბიჯი

VHDL– ში მარტივი ოთხმხრივი კომპლექტი ასოციაციური ქეში კონტროლერის დიზაინი: ჩემს წინა ინსტრუქციებში ჩვენ ვნახეთ, თუ როგორ უნდა შევადგინოთ მარტივი შენახული ქეში კონტროლერი. ამჯერად, ჩვენ წინ მივდივართ. ჩვენ შევქმნით მარტივ ოთხმხრივ მითითებულ ასოციაციურ ქეში კონტროლერს. უპირატესობა? ნაკლები გამოტოვების მაჩვენებელი, მაგრამ შესრულების ფასად

I2C სამაგისტრო დიზაინი VHDL– ში: 5 ნაბიჯი

VHDL– ში I2C სამაგისტრო დიზაინი: ამ ინსტრუქციაში განიხილება VHDL– ში მარტივი I2C სამაგისტრო დიზაინის შექმნა. შენიშვნა: დააწკაპუნეთ თითოეულ სურათზე სრული სურათის სანახავად

Arduino LCD სამაგისტრო საათი: 10 ნაბიჯი (სურათებით)

Arduino LCD სამაგისტრო საათი: ეს საათი შექმნილია როგორც ცალკე საათი ან როგორც სამაგისტრო საათი მონა საათების მართვისთვის და პორტატულია ბატარეის სარეზერვო საშუალებით. იხილეთ საათის ვებსაიტი დამატებითი დეტალებისთვის LCD სამაგისტრო საათი მთავარი გვერდი განახლება- ავტომატური ზაფხულის წინსვლა და ზამთრის ჩამორჩენა

არდუინოზე დაფუძნებული სამაგისტრო საათი სკოლებისთვის: 9 ნაბიჯი (სურათებით)

არდუინოზე დაფუძნებული სამაგისტრო საათი სკოლებისთვის: თუ თქვენი სკოლა, ან საბავშვო სკოლა, ან სხვა მდებარეობა ემყარება ცენტრალურ სამაგისტრო საათს, რომელიც გატეხილია, თქვენ შეიძლება გამოიყენოთ ეს მოწყობილობა. ახალი სამაგისტრო საათები, რა თქმა უნდა, ხელმისაწვდომია, მაგრამ სკოლის ბიუჯეტი უკიდურესი ზეწოლის ქვეშ იმყოფება და ეს მართლაც სატირალია