Სარჩევი:

- ავტორი John Day day@howwhatproduce.com.

- Public 2024-01-30 10:17.

- ბოლოს შეცვლილი 2025-06-01 06:09.

ამ სასწავლო ინსტრუქციაში განიხილება VHDL- ში მარტივი I2C სამაგისტრო დიზაინის შემუშავება.

შენიშვნა: დააწკაპუნეთ თითოეულ სურათზე სრული სურათის სანახავად

ნაბიჯი 1: I2C ავტობუსის მიმოხილვა

• დგას ინტერ ინტეგრირებული სქემისთვის.

• სინქრონული, ნახევრად დუპლექსი.

• ორი მავთულის ინტერფეისი - SDA და SCL.

• SDA - სერიული მონაცემთა ხაზი, რომელსაც აკონტროლებენ Master და Slave

• SCL - სერიული საათი გენერირებული ოსტატის მიერ

• Multi-master, Multi-slave პროტოკოლი.

• ორი რეჟიმი - 100 კბიტი/წმ და 400 კბიტი/წმ: ნელი და სწრაფი.

ნაბიჯი 2: RTL დიზაინი VHDL- ში

ჩვენი I2C ოსტატის დიზაინის მახასიათებლები

- 8 ბიტიანი მონაცემთა ჩარჩო.

- SCL მხოლოდ ცალმხრივი კონტროლი.

- 7-ბიტიანი მონა მისამართი.

- მხარს უჭერს როგორც ნელ, ასევე სწრაფ რეჟიმებს.

- მარტოხელა ბატონი, მრავალ მონა.

- შეესაბამება Philips- ის ორიგინალ I2C სპეციფიკაციებს.

გამოიყენება სუფთა RTL კოდი. ასე რომ, IP არის ადვილად პორტატული ყველა FPGA- ში. კომპაქტური FSM დაფუძნებული დიზაინი შინაგანად გამომუშავებული საათის გამოყენებით უზრუნველყოფს ოპტიმალურ არეს და შესრულებას.

ნაბიჯი 3: სიმულაცია და ტესტირება

სატესტო გარემო

- ფუნქციური სიმულაცია და ტესტირება მესამე მხარის I2C Slave IP გამოყენებით.

- სინთეზირებულია Xilinx Vivado ინსტრუმენტების ნაკრების გამოყენებით.

- დანერგილი და გამოცდილი Artix-7 FPGA დაფაზე.

- დრო დამოწმებული დიზაინი 100 MHz.

- შემოწმებულია ტალღის ფორმები DSO/CRO- ზე.

- წარმატებით გამოსცადა კომუნიკაცია Arduino UNO- სთან, როგორც I2C მონა.

ნაბიჯი 4: მნიშვნელოვანი შენიშვნები

- სამაგისტრო ტესტირებისას I2C Slave IP გამოყენებით, დააკონფიგურირეთ მონა კოდი თქვენი მოთხოვნების შესაბამისად. თქვენ შეიძლება გსურთ შეცვალოთ ნაგულისხმევი საათის სიხშირე და მონა მისამართი. საათის სიხშირე ასევე უნდა იყოს კონფიგურირებული სამაგისტრო კოდში.

- ბორტ ტესტირებისას, არ დაივიწყოთ გამწევი რეზისტორები, რადგან SDA ხაზი არის საერთო გადინება !!! შეამოწმეთ google რეკომენდირებული გამწევი რეზისტორი სხვადასხვა i2c სიჩქარისთვის. მე გამოვიყენე 2.2K 100 kHz- ზე.

- თუ არ იყენებთ საცდელ სკამს და დამოუკიდებლად აყალიბებთ ოსტატს, ფრთხილად მოახდინეთ SDA სიგნალის სიმულაცია, რადგან ეს არის ორმხრივი სიგნალი (შესასვლელი) სიგნალი. მას აქვს ორი მძღოლი, სამაგისტრო და მონა მხარე. თქვენ უნდა იცოდეთ როდის უნდა „აიძულოთ“და როდის „აიძულოთ“.

- SCL არის ცალმხრივი ხაზი. არ არის საჭირო გაყვანა.

- გთხოვთ საფუძვლიანად გაიაროთ IP დოკუმენტაცია.

ნაბიჯი 5: თანდართული ფაილები

- I2C სამაგისტრო ყველა RTL კოდი.

- საცდელი სკამი, I2C Slave კოდები ასევე, ტესტირებისთვის.

- IP დოკუმენტაცია.

ნებისმიერი შეკითხვისთვის, გთხოვთ დამიკავშირდეთ:

მიტუ რაჯი

გამომყევი:

შეკითხვისთვის დაუკავშირდით: iammituraj@gmail.com

გირჩევთ:

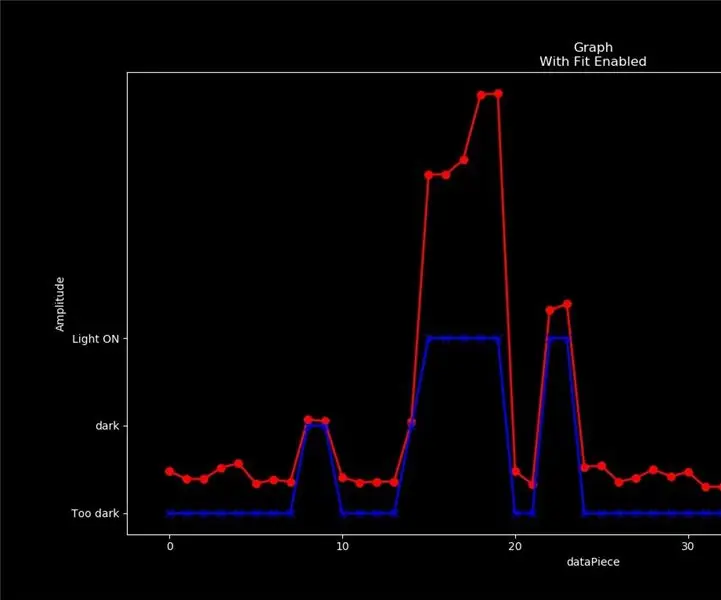

სინათლის ინტენსივობის შეთქმულება არდუინოს და პითონის არდუინოს სამაგისტრო ბიბლიოთეკის გამოყენებით: 5 ნაბიჯი

სინათლის ინტენსივობის შეთქმულება არდუინოს და პითონის არდუინოს სამაგისტრო ბიბლიოთეკის გამოყენებით: არდუინო არის ეკონომიური, მაგრამ მაღალეფექტური და ფუნქციონალური ინსტრუმენტი, ჩაშენებულ C- ში პროგრამირება ხდის პროექტების დამღლელ პროცესს! პითონის Arduino_Master მოდული ამარტივებს ამას და გვაძლევს საშუალებას გამოვთვალოთ, ამოიღოთ ნაგვის მნიშვნელობები

VHDL– ში მარტივი ოთხმხრივი კომპაქტური ქეში კონტროლერის დიზაინი: 4 ნაბიჯი

VHDL– ში მარტივი ოთხმხრივი კომპლექტი ასოციაციური ქეში კონტროლერის დიზაინი: ჩემს წინა ინსტრუქციებში ჩვენ ვნახეთ, თუ როგორ უნდა შევადგინოთ მარტივი შენახული ქეში კონტროლერი. ამჯერად, ჩვენ წინ მივდივართ. ჩვენ შევქმნით მარტივ ოთხმხრივ მითითებულ ასოციაციურ ქეში კონტროლერს. უპირატესობა? ნაკლები გამოტოვების მაჩვენებელი, მაგრამ შესრულების ფასად

SPI სამაგისტრო დიზაინი VHDL– ში: 6 ნაბიჯი

SPI Master– ის დიზაინი VHDL– ში: ამ ინსტრუქციურად, ჩვენ ვაპირებთ VHDL– ში ნულიდან SPI Bus Master– ის შემუშავებას

Arduino LCD სამაგისტრო საათი: 10 ნაბიჯი (სურათებით)

Arduino LCD სამაგისტრო საათი: ეს საათი შექმნილია როგორც ცალკე საათი ან როგორც სამაგისტრო საათი მონა საათების მართვისთვის და პორტატულია ბატარეის სარეზერვო საშუალებით. იხილეთ საათის ვებსაიტი დამატებითი დეტალებისთვის LCD სამაგისტრო საათი მთავარი გვერდი განახლება- ავტომატური ზაფხულის წინსვლა და ზამთრის ჩამორჩენა

არდუინოზე დაფუძნებული სამაგისტრო საათი სკოლებისთვის: 9 ნაბიჯი (სურათებით)

არდუინოზე დაფუძნებული სამაგისტრო საათი სკოლებისთვის: თუ თქვენი სკოლა, ან საბავშვო სკოლა, ან სხვა მდებარეობა ემყარება ცენტრალურ სამაგისტრო საათს, რომელიც გატეხილია, თქვენ შეიძლება გამოიყენოთ ეს მოწყობილობა. ახალი სამაგისტრო საათები, რა თქმა უნდა, ხელმისაწვდომია, მაგრამ სკოლის ბიუჯეტი უკიდურესი ზეწოლის ქვეშ იმყოფება და ეს მართლაც სატირალია