Სარჩევი:

- ავტორი John Day day@howwhatproduce.com.

- Public 2024-01-30 10:18.

- ბოლოს შეცვლილი 2025-06-01 06:09.

ამ ინსტრუქციურად, ჩვენ ვაპირებთ შევქმნათ მარტივი VGA კონტროლერი RTL- ში. VGA კონტროლერი არის ციფრული წრე, რომელიც შექმნილია VGA დისპლეების მართვისთვის. ის იკითხება ჩარჩო ბუფერიდან (VGA მეხსიერება), რომელიც წარმოადგენს ჩვენების ჩარჩოს და ქმნის საჭირო მონაცემებს და სინქრონიზაციის სიგნალებს ჩვენების მიზნით.

თუ თქვენ ეძებთ Verilog/System verilog კოდს: ეწვიეთ ჩემს ბლოგს VGA კონტროლერს და ვიდეო სისტემას Verilog- ში

ნაბიჯი 1: VGA კონტროლერის ინტერფეისი

ქვემოთ მოცემულია VGA კონტროლერის მთავარი ინტერფეისის სიგნალები

- Pixel საათი ან VGA საათი

- HSYNC და VSYNC სიგნალები

არჩეული VGA ეკრანისთვის, თქვენ ჯერ უნდა გამოთვალოთ Pixel Clock- ის სიხშირე, რომელიც საჭიროა მისი მართვისთვის. ეს დამოკიდებულია 3 პარამეტრზე: სულ ჰორიზონტალური პიქსელი, სულ ვერტიკალური პიქსელი, ეკრანის განახლების მაჩვენებელი.

როგორც წესი, F = THP * TVP * განახლების მაჩვენებელი

იპოვეთ დოკუმენტაცია პიქსელის საათის შესახებ, რომელიც საჭიროა სხვადასხვა VGA დისპლეისთვის, თანდართულ RAR- ში.

HSYNC და VSYNC სიგნალები წარმოიქმნება Pixel საათიდან. HSYNC და VSYNC სიგნალების დრო დამოკიდებულია პარამეტრების რაოდენობაზე: ჰორიზონტალური და ვერტიკალური წინა ღერი, ჰორიზონტალური და ვერტიკალური ზურგჩანთა, ჰორიზონტალური და ვერტიკალური ჩვენების პიქსელები, ჰორიზონტალური და ვერტიკალური სინქრონიზაციის პულსის სიგანე და პოლარობა.

ეს პარამეტრები სტანდარტიზებულია არჩეული VGA დისპლეისთვის. იპოვეთ ეს დოკუმენტები თანდართულ RAR- ში.

ეს პარამეტრები არის კონფიგურირებადი პარამეტრები ჩვენს VGA კონტროლერის IP- ში.

ნაბიჯი 2: VGA კონტროლერის ინტეგრირება VGA დისპლეით

ფიგურა გვიჩვენებს, თუ როგორ ხდება VGA კონტროლერის ინტეგრირება VGA დისპლეით. სისტემის დასასრულებლად გჭირდებათ კიდევ ორი კომპონენტი:

- ჩარჩოს ბუფერი: მეხსიერება, რომელიც ინახავს ჩარჩოს ჩვენებას.

- ვიდეო DAC: DAC, რომელიც გარდაქმნის RGB ციფრულ მონაცემებს და მართავს VGA ჩვენებას RGB ანალოგური სიგნალებით შესაბამის ძაბვის დონეზე.

ერთ -ერთი ყველაზე მარტივი და პოპულარული ვიდეო DAC არის ADV7125. ეს არის 8 ბიტიანი DAC, რომელიც გარდაქმნის RGB ციფრულ სიტყვებს 0-0,7 V ანალოგურ სიგნალებად და მართავს VGA ეკრანს.

ნაბიჯი 3: ჩარჩოს ბუფერის დიზაინი

ეს არის მეხსიერება, რომელიც 'ინახავს' გამოსახულების ჩვენებას. როგორც წესი, ეს არის RAM ან ზოგჯერ ROM. ჩვენ განვიხილავთ, თუ როგორ უნდა შეიქმნას ჩარჩო ბუფერი გამოსახულების წარმოსადგენად. ჩარჩო ბუფერი გადასცემს ამ ციფრულ ინფორმაციას ვიდეო DAC- ზე VGA კონტროლერის ბრძანებით.

პირველ რიგში, ჩვენ უნდა განვსაზღვროთ პიქსელის საჭირო სიღრმე. ის წყვეტს სურათის ხარისხს, პიქსელის ფერის მრავალფეროვნებას. 8 ბიტიანი DAC- სთვის, ჩვენ უნდა წარმოვადგინოთ პიქსელის ძირითადი ფერის კომპონენტები: R, G და B თითოეული 8 ბიტებში. ეს ნიშნავს, რომ პიქსელი არის 24 ბიტიანი.

თითოეული პიქსელი ინახება მიმდებარედ Frame Buffer მეხსიერების ადგილებში.

დავუშვათ, რომ გამოსახული სურათი არის 800x600 პიქსელი.

ამიტომ ჩარჩო ბუფერი საჭიროა 800x600 = 480000 x 24 ბიტიანი მეხსიერებით

მეხსიერების საერთო ზომაა 800x600x24 = 1400 კბ დაახლ.

თუ შავი და თეთრი სურათია, 800x600x1 = 60 კბ დაახ.

შესაძლოა დაბლოკოს ოპერატიული მეხსიერება Xilinx FPGA- ში Frame Buffer- ის წარმოსადგენად.

ნაბიჯი 4: შენიშვნები

- დამატებითი სიგნალები საჭიროა VGA კონტროლერზე, არჩეული DAC- ის მიხედვით. მე გამოვიყენე ADV7125.

- დაამატეთ ციკლის შეფერხებები VSYNC- სა და HSYNC- ზე VGA ეკრანის მართვამდე. ეს გამოწვეულია DAC და მეხსიერების დაყოვნებით. პიქსელის სიგნალები უნდა იყოს სინქრონიზებული HSYNC და VSYNC. ჩემს შემთხვევაში, ეს იყო 2 ციკლის შეფერხება.

- თუ მოცემული ზომის ჩარჩო ბუფერი არ შეიძლება დაპროექტდეს FPGA- ზე ბლოკის მოცულობის შეზღუდვის გამო, გამოიყენეთ მცირე მეხსიერება გამოსახულების გამოსახატად და უბრალოდ შეასწორეთ კოდი, რომ გადაახვიოთ მისამართი არსებული მეხსიერების საზღვარზე და არა სრული ჩარჩოს საზღვარზე. ეს იმეორებს ერთსა და იმავე სურათს მთელ ეკრანზე. კიდევ ერთი მეთოდი არის პიქსელის მასშტაბირება, რომლის დროსაც თითოეული პიქსელი მეორდება, რომ მთლიანი გამოსახულება აჩვენოს სრულ ეკრანზე, ნაკლები გარჩევადობით. ეს შეიძლება გაკეთდეს კოდში მისამართის გაზრდის ლოგიკის შეცვლით.

- IP არის სრულიად პორტატული ყველა FPGA- ზე და დრო დამოწმებულია 100 MHz- მდე Virtex-4 FPGA- ზე.

ნაბიჯი 5: თანდართული ფაილები

RAR შეიცავს:

- VGA კონტროლერის კოდი

- VGA სტანდარტების PDF ფაილები.

გირჩევთ:

VHDL– ში მარტივი ოთხმხრივი კომპაქტური ქეში კონტროლერის დიზაინი: 4 ნაბიჯი

VHDL– ში მარტივი ოთხმხრივი კომპლექტი ასოციაციური ქეში კონტროლერის დიზაინი: ჩემს წინა ინსტრუქციებში ჩვენ ვნახეთ, თუ როგორ უნდა შევადგინოთ მარტივი შენახული ქეში კონტროლერი. ამჯერად, ჩვენ წინ მივდივართ. ჩვენ შევქმნით მარტივ ოთხმხრივ მითითებულ ასოციაციურ ქეში კონტროლერს. უპირატესობა? ნაკლები გამოტოვების მაჩვენებელი, მაგრამ შესრულების ფასად

პროგრამირებადი შეფერხების კონტროლერის დიზაინი VHDL– ში: 4 ნაბიჯი

VHDL– ში პროგრამირებადი შეფერხების კონტროლერის დიზაინი: მე აღფრთოვანებული ვარ ამ ბლოგის პასუხებით. მადლობა ბიჭებს, რომ ეწვიეთ ჩემს ბლოგს და მოტივაცია მომეცით გაგიზიაროთ ჩემი ცოდნა. ამჯერად, მე წარმოგიდგენთ კიდევ ერთი საინტერესო მოდულის დიზაინს, რომელსაც ყველა SOC– ში ვხედავთ - Interrupt C

მარტივი ქეში კონტროლერის დიზაინი VHDL– ში: 4 ნაბიჯი

მარტივი ქეში კონტროლერის დიზაინი VHDL– ში: მე ვწერ ამას სასწავლებლად, რადგან ცოტა გამიჭირდა რაიმე საცნობარო VHDL კოდის მოპოვება, რომ ვისწავლო და დავიწყო ქეში კონტროლერის დიზაინი. ასე რომ, მე თვითონ შევქმენი ქეში კონტროლერი ნულიდან და წარმატებით გამოვცადე FPGA– ზე. მე მაქვს პ

PCB დიზაინი მარტივი და მარტივი ნაბიჯებით: 30 ნაბიჯი (სურათებით)

PCB დიზაინი მარტივი და მარტივი ნაბიჯებით: HELLO FRIENDS მისი ძალიან სასარგებლო და მარტივი სამეურვეო პროგრამა მათთვის, ვისაც სურს ისწავლოს PCB დიზაინის სწავლა

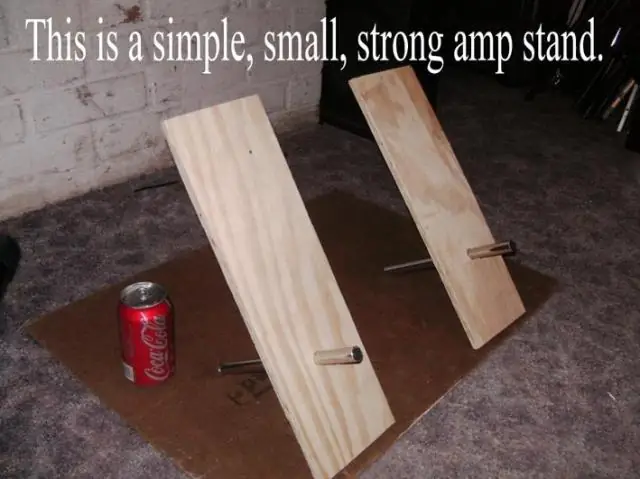

გიტარის გამაძლიერებელი დახრის სადგამი - "აფრიკული სკამის" დიზაინი - მარტივი, პატარა, ძლიერი, მარტივი, უფასო ან რეალური იაფი: 9 ნაბიჯი

გიტარის გამაძლიერებელი დახრის სადგამი - "აფრიკული სავარძლის" დიზაინი - მარტივი, პატარა, ძლიერი, მარტივი, უფასო ან რეალური იაფი: გიტარის გამაძლიერებლის დახრის სადგამი - ძალიან ადვილი - მარტივი, პატარა, ძლიერი, უფასო ან რეალური იაფი. ყველა ზომის ამპერისთვის, თუნდაც დიდი კაბინეტები ცალკე თავით. უბრალოდ გააკეთეთ დაფები და მილები ზომის და გჭირდებათ თითქმის ნებისმიერი აღჭურვილობა, რომელიც გსურთ