Სარჩევი:

- ავტორი John Day day@howwhatproduce.com.

- Public 2024-01-30 10:17.

- ბოლოს შეცვლილი 2025-06-01 06:09.

მე ვწერ ამას სასწავლებლად, რადგან ცოტა გამიჭირდა რაიმე საცნობარო VHDL კოდის მოპოვება, რომ ვისწავლო და დავიწყო ქეში კონტროლერის დიზაინი. ასე რომ, მე თვითონ შევქმენი ქეში კონტროლერი ნულიდან და წარმატებით გამოვცადე FPGA- ზე. მე აქ წარმოვადგინე მარტივი რუქის ქეშიანი კონტროლერი, ისევე როგორც მთელი პროცესორი-მეხსიერების სისტემის მოდელირებული ქეში კონტროლერის შესამოწმებლად. ვიმედოვნებ, რომ ეს ინსტრუქცია თქვენთვის სასარგებლოა, როგორც მითითება თქვენი ქეში კონტროლერების შესაქმნელად.

ნაბიჯი 1: სპეციფიკაციები

ეს არის Cache Controller- ის ძირითადი სპეციფიკაციები, რომლის შექმნასაც ჩვენ ვაპირებთ:

- პირდაპირი რუქაზე. (გადადით ამ ბმულზე, თუ ეძებთ ასოცირებული რუქის ქეში კონტროლერს)

- ერთჯერადი ბანკი, ბლოკირების ქეში.

- დაწერეთ პოლიტიკა დაწერეთ ჰიტები.

- გამოტოვების გამოტოვების გამოტოვება გამოუქვეყნებელი ან ჩაწერეთ.

- არ არის დაწერილი ბუფერი ან სხვა ოპტიმიზაცია.

- ტეგების მასივი ჩართულია.

გარდა ამისა, ჩვენ შევქმნით Cache მეხსიერებას და მთავარ მეხსიერების სისტემასაც.

Cache მეხსიერების ნაგულისხმევი (კონფიგურირებადი) სპეციფიკაციები:

- 256 ბაიტი ერთჯერადი ბანკის ქეში.

- 16 ქეში ხაზი, თითოეული ქეში ხაზი (ბლოკი) = 16 ბაიტი.

ძირითადი მეხსიერების მახასიათებლები:

- სინქრონული წაკითხვის/ჩაწერის მეხსიერება.

- მრავალბანკიანი გადახურული მეხსიერება - ოთხი მეხსიერების ბანკი.

- თითოეული ბანკის ზომა = 1 კბ თითოეული. აქედან გამომდინარე, საერთო ზომა = 4 კბ.

- Word (4 Bytes) მისამართის მეხსიერება 10-ბიტიანი მისამართის ავტობუსით.

- უფრო მაღალი გამტარობა წაკითხვისთვის. წაიკითხეთ მონაცემთა სიგანე = 16 ბიტი ერთ საათის ციკლში.

- ჩაწერეთ მონაცემთა სიგანე = 4 ბიტი.

შენიშვნა: შეამოწმეთ ჩემი ახალი ინსტრუქცია, თუ თქვენ ეძებთ 4-გზის ასოციაციური ქეში კონტროლერის დიზაინს

ნაბიჯი 2: მთელი სისტემის RTL ხედი

ზედა მოდულის სრული RTL წარმოდგენა ნაჩვენებია ფიგურაში (პროცესორის გამოკლებით). ავტობუსების სტანდარტული მახასიათებლებია:

- ყველა მონაცემთა ავტობუსი არის 32 ბიტიანი ავტობუსი.

- მისამართის ავტობუსი = 32 ბიტიანი ავტობუსი (მაგრამ მეხსიერების საშუალებით აქ მხოლოდ 10 ბიტია მიმართული).

- მონაცემთა ბლოკი = 128 ბიტი (ფართო გამტარუნარიანობის ავტობუსი წაკითხვისთვის).

- ყველა კომპონენტი ერთსა და იმავე საათს მართავს.

ნაბიჯი 3: გარემოს გამოცდა

ზედა მოდული შემოწმდა Test Bench- ის გამოყენებით, რომელიც უბრალოდ აყალიბებს არა მილსადენის პროცესორს (რადგან მთლიანი პროცესორის დაპროექტება სულაც არ არის ადვილი !!). საცდელი მაგიდა ხშირად წარმოქმნის წაკითხვის/ჩაწერის მონაცემებს მეხსიერებაში. ეს დასცინის ტიპიურ "Load" და "Store" ინსტრუქციებს, რომლებიც გავრცელებულია პროცესორის მიერ შესრულებულ ყველა პროგრამაში. ტესტის შედეგებმა წარმატებით დაადასტურა ქეში კონტროლერის ფუნქციონირება. ქვემოთ მოცემულია ტესტის სტატისტიკა:

- ყველა წაკითხვის/ჩაწერის Miss და Hit სიგნალები სწორად იქნა გენერირებული.

- ყველა წაკითხვის/ჩაწერის მონაცემების ოპერაცია წარმატებული იყო.

- მონაცემთა შეუსაბამობა/შეუსაბამობა არ არის გამოვლენილი.

- დიზაინი წარმატებით იქნა დადასტურებული დროის მაქსიმუმისთვის. საათის სიხშირე = 110 MHz Xilinx Virtex-4 ML-403 დაფაზე (მთელი სისტემა), 195 MHz მხოლოდ Cache Controller- ისთვის.

- ბლოკის ოპერატიული მეხსიერება გამოითვლება ძირითადი მეხსიერებისათვის. ყველა სხვა მასივი განხორციელდა LUT- ებზე.

ნაბიჯი 4: თანდართული ფაილები

შემდეგი ფაილები ერთვის აქ ამ ბლოგს:

- . VHD ფაილები Cache Controller, Cache Data Array, Main Memory System.

- საცდელი სკამი.

- დოკუმენტაცია ქეში კონტროლერის შესახებ.

შენიშვნები:

- გაიარეთ დოკუმენტაცია, რომ გაიგოთ აქ წარმოდგენილი ქეში კონტროლერის სპეციფიკაციები.

- კოდის ნებისმიერი ცვლილება დამოკიდებულია სხვა მოდულებზე. ასე რომ, ცვლილებები გონივრულად უნდა მოხდეს. ყურადღება მიაქციეთ ჩემს მიერ გამოქვეყნებულ ყველა კომენტარს და სათაურს.

- თუ რაიმე მიზეზის გამო, ბლოკის ოპერატიული მეხსიერება არ არის გამოთვლილი ძირითადი მეხსიერებისათვის, შეამცირეთ მეხსიერების ზომა, რასაც მოჰყვება მისამართების ავტობუსის სიგანეების ცვლილებები ფაილებში და ასე შემდეგ. ასე რომ ერთი და იგივე მეხსიერება შეიძლება განხორციელდეს როგორც LUT- ებზე, ასევე განაწილებულ RAM- ზე. ეს დაზოგავს მარშრუტის დროს და რესურსებს. ან, გადადით FPGA- ს კონკრეტულ დოკუმენტაციაში და იპოვეთ ბლოკის RAM- ის თავსებადი კოდი და შესაბამისად შეცვალეთ კოდი და გამოიყენეთ იგივე მისამართის ავტობუსის სიგანის სპეციფიკაციები. იგივე ტექნიკა Altera FPGA- სთვის.

გირჩევთ:

VHDL– ში მარტივი ოთხმხრივი კომპაქტური ქეში კონტროლერის დიზაინი: 4 ნაბიჯი

VHDL– ში მარტივი ოთხმხრივი კომპლექტი ასოციაციური ქეში კონტროლერის დიზაინი: ჩემს წინა ინსტრუქციებში ჩვენ ვნახეთ, თუ როგორ უნდა შევადგინოთ მარტივი შენახული ქეში კონტროლერი. ამჯერად, ჩვენ წინ მივდივართ. ჩვენ შევქმნით მარტივ ოთხმხრივ მითითებულ ასოციაციურ ქეში კონტროლერს. უპირატესობა? ნაკლები გამოტოვების მაჩვენებელი, მაგრამ შესრულების ფასად

პროგრამირებადი შეფერხების კონტროლერის დიზაინი VHDL– ში: 4 ნაბიჯი

VHDL– ში პროგრამირებადი შეფერხების კონტროლერის დიზაინი: მე აღფრთოვანებული ვარ ამ ბლოგის პასუხებით. მადლობა ბიჭებს, რომ ეწვიეთ ჩემს ბლოგს და მოტივაცია მომეცით გაგიზიაროთ ჩემი ცოდნა. ამჯერად, მე წარმოგიდგენთ კიდევ ერთი საინტერესო მოდულის დიზაინს, რომელსაც ყველა SOC– ში ვხედავთ - Interrupt C

მარტივი VGA კონტროლერის დიზაინი VHDL და Verilog– ში: 5 ნაბიჯი

მარტივი VGA კონტროლერის დიზაინი VHDL– ში და Verilog– ში: ამ ინსტრუქციურად, ჩვენ ვაპირებთ შევქმნათ მარტივი VGA კონტროლერი RTL– ში. VGA კონტროლერი არის ციფრული წრე, რომელიც შექმნილია VGA დისპლეების მართვისთვის. ის იკითხება ჩარჩო ბუფერიდან (VGA მეხსიერება), რომელიც წარმოადგენს ჩვენების ჩარჩოს და ქმნის საჭირო

PCB დიზაინი მარტივი და მარტივი ნაბიჯებით: 30 ნაბიჯი (სურათებით)

PCB დიზაინი მარტივი და მარტივი ნაბიჯებით: HELLO FRIENDS მისი ძალიან სასარგებლო და მარტივი სამეურვეო პროგრამა მათთვის, ვისაც სურს ისწავლოს PCB დიზაინის სწავლა

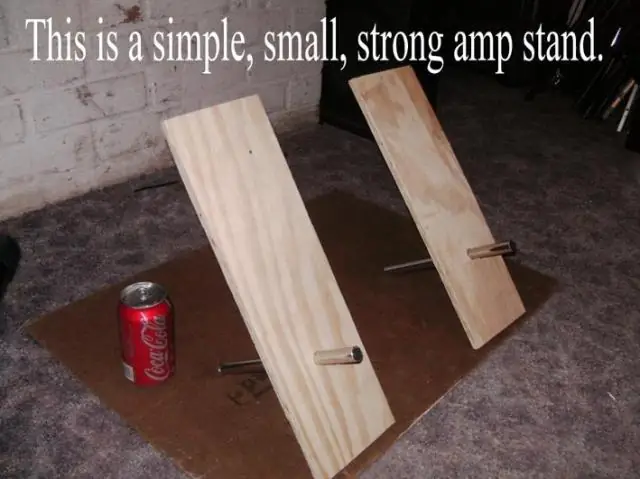

გიტარის გამაძლიერებელი დახრის სადგამი - "აფრიკული სკამის" დიზაინი - მარტივი, პატარა, ძლიერი, მარტივი, უფასო ან რეალური იაფი: 9 ნაბიჯი

გიტარის გამაძლიერებელი დახრის სადგამი - "აფრიკული სავარძლის" დიზაინი - მარტივი, პატარა, ძლიერი, მარტივი, უფასო ან რეალური იაფი: გიტარის გამაძლიერებლის დახრის სადგამი - ძალიან ადვილი - მარტივი, პატარა, ძლიერი, უფასო ან რეალური იაფი. ყველა ზომის ამპერისთვის, თუნდაც დიდი კაბინეტები ცალკე თავით. უბრალოდ გააკეთეთ დაფები და მილები ზომის და გჭირდებათ თითქმის ნებისმიერი აღჭურვილობა, რომელიც გსურთ