Სარჩევი:

- ავტორი John Day day@howwhatproduce.com.

- Public 2024-01-30 10:16.

- ბოლოს შეცვლილი 2025-06-01 06:09.

შეაერთეთ თქვენი Mojo დეველოპმენტის დაფა გარე საშუალებებთან ამ ფარით.

რა არის მოჯოს განვითარების დაფა?

Mojo- ს განვითარების დაფა არის განვითარების დაფა, რომელიც დაფუძნებულია Xilinx spartan 3 FPGA- ს გარშემო. დაფა დამზადებულია ალჩიტრიის მიერ. FPGA ძალიან სასარგებლოა იქ, სადაც რამდენიმე პროცესი ერთდროულად უნდა შესრულდეს.

რა დაგჭირდება?

მარაგები

მოჯოს განვითარების დაფა

გერბერის ფაილი

8 x 15k ohm რეზისტორები (სურვილისამებრ*)

4 x 470 ohm რეზისტორები

4 x 560 ohm რეზისტორები

4 x CC შვიდი სეგმენტის ჩვენება

4 x 3 მმ LED ნათურები

4 x SPDT ტაქტილური გადამრთველი

1 x 4 პოზიციის ზედაპირზე დამაგრების DIP გადამრთველი

2 x 25 2 ან 4 x 25 თავით

1x 2 x 5 pin ყუთის თავი

გასაყიდი რკინა

Solder

ნაკადი

*(თუ ეს რეზისტორები გამოტოვებულია შიდა ამოღება/ამოღება უნდა იყოს ჩართული შესაბამისი ქინძისთავებისთვის)

ნაბიჯი 1: ატვირთეთ გერბერი თქვენი არჩევანის Pcb მწარმოებელზე

ჩემი დაფებისთვის მე შევუკვეთე JLC PCB- დან.

ერთადერთი ცვლილება, რაც მე გავაკეთე, იყო ფერი, რომელიც მინდოდა მოჯოს შავთან შეხამება.

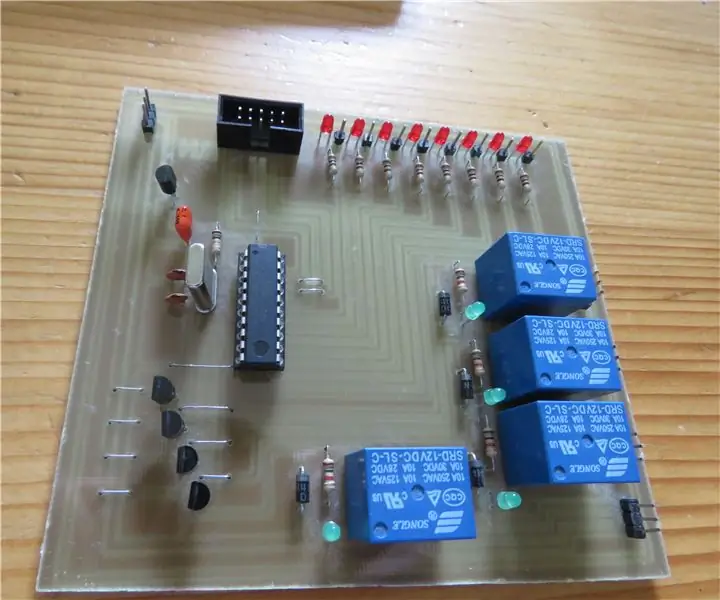

ნაბიჯი 2: გამგეობის ასამბლეა

როდესაც შედუღების მე ყოველთვის სასარგებლოა შედუღების ქვედა ნაწილები პირველი ასე რომ დაიწყოს რეზისტორების არის კარგი იდეა.

R5, R6, R7, R8, R9, R10, R11 და R12 არის 15k ohm რეზისტორები, რომლებიც გამოიყენება გადამრთველების ჩამოსაყვანად (თუ თქვენ იყენებთ შიდა ამოღებას/პულდუნს, იგნორირება გაუკეთეთ ამას).

R1, R2, R3, R4 არის 560 ohm რეზისტორები, რომლებიც პასუხისმგებელნი არიან დენის შეზღუდვაზე 7 სეგმენტის ეკრანის საშუალებით.

R13, R14, R15, R16 არის 470 ohm რეზისტორები, რომლებიც პასუხისმგებელნი არიან 4 LED- ის საშუალებით დენის შეზღუდვაზე.

შემდეგ შეაერთეთ დიპლომატიური გადამრთველი, ტაქტილური კონცენტრატორები, LED- ები, შვიდი სეგმენტის დისპლეი და ყუთის სათაურის კონექტორი ამ თანმიმდევრობით.

ახლა მოათავსეთ 25 -იანი 2 -ით (ან 2 25 -ით 1 -ით) მოჯოში, ქინძისთავების გასწორების მიზნით. ფარის გასწორება ქინძისთავებით და შედუღებით ადგილზე.

ნაბიჯი 3: პროგრამული უზრუნველყოფის დაყენება

Alchitry ვებსაიტზე მითითებული პროგრამული უზრუნველყოფისთვის გაცნობებთ, რა გჭირდებათ დასაწყებად და დააინსტალირეთ Xilinx ISE. თუმცა.ucf ფაილის შეცვლა ისე, რომ მან იცოდეს რა ქინძისთავები არის დაკავშირებული რა მნიშვნელოვანია თქვენი პროგრამის გასაშვებად.

აქ არის.ucf ფაილი, რომელსაც ფარს ვიყენებ:

კონფიგურაცია VCCAUX = 3.3;

NET "clk" TNM_NET = clk; TIMESPEC TS_clk = პერიოდი "clk" 50 MHz HIGH 50%; NET "clk" LOC = P56 | IOSTANDARD = LVTTL; NET "rst_n" LOC = P38 | IOSTANDARD = LVTTL; NET "cclk" LOC = P70 | IOSTANDARD = LVTTL; NET "spi_mosi" LOC = P44 | IOSTANDARD = LVTTL; NET "spi_miso" LOC = P45 | IOSTANDARD = LVTTL; NET "spi_ss" LOC = P48 | IOSTANDARD = LVTTL; NET "spi_sck" LOC = P43 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P46 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P61 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P62 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P65 | IOSTANDARD = LVTTL; NET "avr_tx" LOC = P55 | IOSTANDARD = LVTTL; NET "avr_rx" LOC = P59 | IOSTANDARD = LVTTL; NET "avr_rx_busy" LOC = P39 | IOSTANDARD = LVTTL; NET "Q [0]" LOC = P26 | IOSTANDARD = LVTTL; NET "Q [1]" LOC = P23 | IOSTANDARD = LVTTL; NET "Q [2]" LOC = P21 | IOSTANDARD = LVTTL; NET "Q [3]" LOC = P16 | IOSTANDARD = LVTTL; NET "S [0]" LOC = P7 | IOSTANDARD = LVTTL; NET "S [1]" LOC = P9 | IOSTANDARD = LVTTL; NET "S [2]" LOC = P11 | IOSTANDARD = LVTTL; NET "S [3]" LOC = P14 | IOSTANDARD = LVTTL; NET "pb [1]" LOC = P30 | IOSTANDARD = LVTTL; NET "pb [2]" LOC = P27 | IOSTANDARD = LVTTL; NET "pb [3]" LOC = P24 | IOSTANDARD = LVTTL; NET "pb [4]" LOC = P22 | IOSTANDARD = LVTTL; NET "სევსეგა [0]" LOC = P57 | IOSTANDARD = LVTTL; NET "sevsegb [0]" LOC = P58 | IOSTANDARD = LVTTL; NET "sevsegc [0]" LOC = P66 | IOSTANDARD = LVTTL; NET "sevsegd [0]" LOC = P67 | IOSTANDARD = LVTTL; NET "sevsege [0]" LOC = P74 | IOSTANDARD = LVTTL; NET "sevsegf [0]" LOC = P75 | IOSTANDARD = LVTTL; NET "sevsegg [0]" LOC = P78 | IOSTANDARD = LVTTL; NET "sevsegdp [0]" LOC = P80 | IOSTANDARD = LVTTL; NET "სევსეგა [1]" LOC = P82 | IOSTANDARD = LVTTL; NET "sevsegb [1]" LOC = P83 | IOSTANDARD = LVTTL; NET "sevsegc [1]" LOC = P84 | IOSTANDARD = LVTTL; NET "sevsegd [1]" LOC = P85 | IOSTANDARD = LVTTL; NET "sevsege [1]" LOC = P87 | IOSTANDARD = LVTTL; NET "sevsegf [1]" LOC = P88 | IOSTANDARD = LVTTL; NET "sevsegg [1]" LOC = P92 | IOSTANDARD = LVTTL; NET "sevsegdp [1]" LOC = P94 | IOSTANDARD = LVTTL; NET "სევსეგა [2]" LOC = P97 | IOSTANDARD = LVTTL; NET "sevsegb [2]" LOC = P98 | IOSTANDARD = LVTTL; NET "sevsegc [2]" LOC = P99 | IOSTANDARD = LVTTL; NET "sevsegd [2]" LOC = P100 | IOSTANDARD = LVTTL; NET "sevsege [2]" LOC = P101 | IOSTANDARD = LVTTL; NET "sevsegf [2]" LOC = P102 | IOSTANDARD = LVTTL; NET "sevsegg [2]" LOC = P104 | IOSTANDARD = LVTTL; NET "sevsegdp [2]" LOC = P111 | IOSTANDARD = LVTTL; NET "სევსეგა [3]" LOC = P114 | IOSTANDARD = LVTTL; NET "sevsegb [3]" LOC = P115 | IOSTANDARD = LVTTL; NET "sevsegc [3]" LOC = P116 | IOSTANDARD = LVTTL; NET "sevsegd [3]" LOC = P117 | IOSTANDARD = LVTTL; NET "sevsege [3]" LOC = P118 | IOSTANDARD = LVTTL; NET "sevsegf [3]" LOC = P119 | IOSTANDARD = LVTTL; NET "sevsegg [3]" LOC = P1120 | IOSTANDARD = LVTTL; NET "sevsegdp [3]" LOC = P121 | IOSTANDARD = LVTTL;

დაიმახსოვრეთ, თუ თქვენ არ გაქვთ დაყენებული დამცავი რეზისტორები.ucf- ში ქინძისთავების შესასწორებლად

| ᲓᲐᲐᲜᲒᲠᲘᲔᲗ; ო

| PULLUP;

თუ გსურთ გამოიყენოთ ბლოკი არაფერში, კავშირები შემდეგია. მარცხნივ არის ბლოკის პინის ნომერი და მარჯვნივ არის მოჯო პინის ნომერი, რომელიც უნდა მიანიჭოთ თქვენს.ucf:

pin 1 = 29

pin 2 = 51

pin 3 = 32

pin 4 = 41

pin 5 = 34

pin 6 = 35

pin 7 = 40

pin 8 = 33

pin 9 = GND

pin 10 = +V

გირჩევთ:

DIY ESP32 განვითარების დაფა - ESPer: 5 ნაბიჯი (სურათებით)

DIY ESP32 განვითარების დაფა - ESPer: ამ ბოლო დროს მე ვკითხულობდი ბევრ IoT– ს (ნივთების ინტერნეტი) და მერწმუნეთ, მე უბრალოდ ვერ მოვითმინე ერთი ამ შესანიშნავი მოწყობილობის შესამოწმებლად, ინტერნეტით დაკავშირების უნარით, მე თვითონ ვიღებ მუშაობას. საბედნიეროდ, შესაძლებლობა

შექმენით თქვენი საკუთარი განვითარების დაფა მიკროკონტროლით: 3 ნაბიჯი (სურათებით)

შექმენით თქვენი საკუთარი განვითარების დაფა მიკროკონტროლით: გსურდათ ოდესმე საკუთარი განვითარების დაფის გაკეთება მიკროკონტროლით და არ იცოდით როგორ. ამ ინსტრუქციურად მე გაჩვენებთ როგორ გააკეთოთ ის. ყველაფერი რაც თქვენ გჭირდებათ არის ელექტრონიკის ცოდნა, სქემების დაპროექტება და პროგრამირება. თუ თქვენ გაქვთ რაიმე ქვესტი

Flappy Bird თამაშის თამაში M5stack Esp32 დაფუძნებული M5stick C განვითარების დაფით: 5 ნაბიჯი

Flappy Bird თამაშის თამაში M5stack Esp32 დაფუძნებული M5stick C განვითარების დაფით: გამარჯობა ბიჭებო დღეს ჩვენ ვისწავლით თუ როგორ უნდა ატვირთოთ flappy bird თამაშის კოდი m5stack– ის მიერ მოწოდებული m5stick c განვითარების დაფაზე. ამ პატარა პროექტისათვის დაგჭირდებათ შემდეგი ორი რამ: m5stick-c განვითარების დაფა: https://www.utsource.net/itm/p/8663561.h

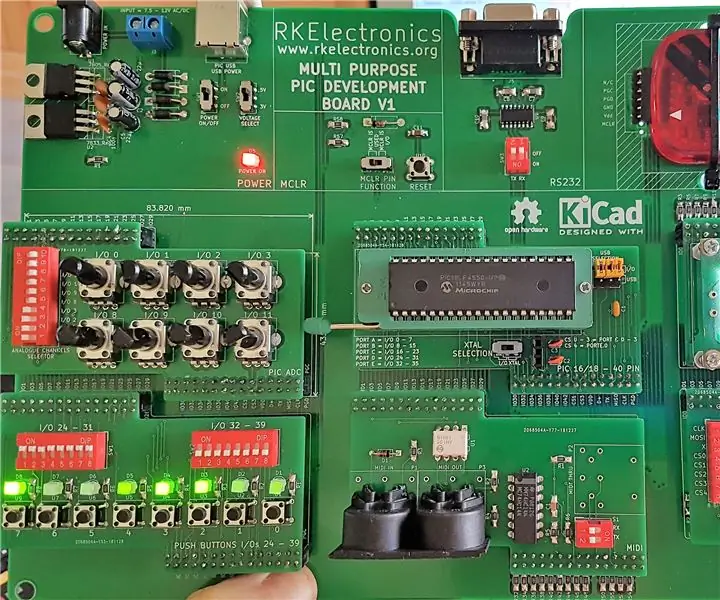

მიკროკონტროლერების განვითარების დაფის დიზაინი: 14 ნაბიჯი (სურათებით)

მიკროკონტროლერების განვითარების დაფის შემუშავება: ხართ თუ არა შემქმნელი, მოყვარული ან ჰაკერი, რომელიც დაინტერესებულია პერფორდის პროექტებიდან, DIP IC– ებიდან და სახლისგან დამზადებული PCB– ებიდან მრავალსართულიანი PCB– ებისთვის, დამზადებული გამგეობის სახლებით და SMD შეფუთვით, რომელიც მზად არის მასობრივი წარმოებისთვის? მაშინ ეს ინსტრუქცია თქვენთვისაა! ეს სახელმძღვანელო

PIC მიკროკონტროლერის განვითარების დაფის სისტემა: 3 ნაბიჯი

PIC მიკროკონტროლერების განვითარების დაფის სისტემა: ეს პროექტი განკუთვნილია PIC– ის განვითარების ინსტრუმენტის შემუშავებისა და გამოყენებისათვის, რომელიც მოქნილია PIC– ზე დაფუძნებული ელექტრონული პროექტების ფართო სპექტრზე. ხშირად უფრო ადვილია მიკროკონტროლის პროექტების შემუშავება განვითარების ინსტრუმენტების გამოყენებით; რაც მომხმარებელზე დაფუძნებული